ANONYMOUS wrote:

> ...I would assume that a data bus will only occur when a process executes a "reading" or "writing" system-call, since a data-bus is omly used to transfer information through specific and different locations, such as sending information into the hard disk or terminal. And from that, I would not think a data-bus will be acquired whilst the rest of the system calls are executed, especially during the execution of "wait" and "exit".

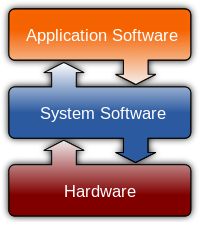

Firstly, a data-bus is a *physical thing*, it's not a verb, or an event, or an action, and in our simple system there's only one of them which connects the CPU, devices, and RAM together. Only one device can perform a data-transfer at any one time, we call that device the owner of the data-bus, and so any device wishing to use the data-bus must first acquire ('get', 'own') the data-bus before starting its I/O transfer.

Only the

read and

write system calls require the data-bus.

> I also want to clarify my suspicions. So, I asked ChatGPT .....

My strongest suggestion is not to use ChatGPT in hoping to 'solve' this. It would take me longer to explain where ChatGPT's answer is wrong, than to write what I have, above. And if you hit 'Regenerate', it'll give another slightly different wrong answer.

Re-read what the project sheet states about the data-bus, watch the (verbose) sample solution to see how time advances when one, and then multiple, processes call

read or

write, and then queue up to first acquire and then use the data-bus.